# HEWLETT-PACKARD JOURNAL August 1992

# HEWLETT-PACKARD JOURNAL

# Articles

1

5

| 6  | <b>Midrange PA-RISC Workstations with Price/Performance Leadership</b> , by Andrew J. DeBaets<br>and Kathleen M. Wheeler                                                            |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 9  | HP 9000 Series 700 Workstation Firmware                                                                                                                                             |  |

| 2  | <b>VLSI Circuits for Low-End and Midrange PA-RISC Computers,</b> by Craig A. Gleason, Leith Johnson, Steven T. Mangelsdorf, Thomas O. Meyer, and Mark A. Forsyth                    |  |

| 1  | PA-RISC Performance Modeling and Simulation                                                                                                                                         |  |

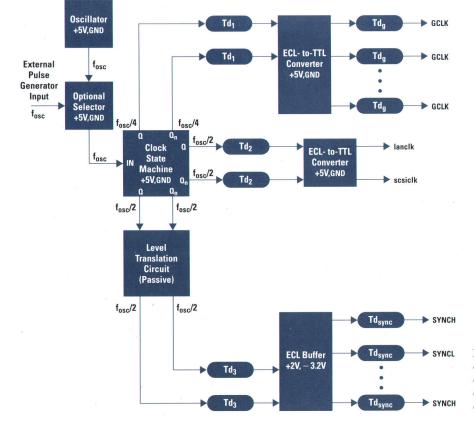

| 3  | ECL Clocks for High-Performance RISC Workstations, by Frank J. Lettang                                                                                                              |  |

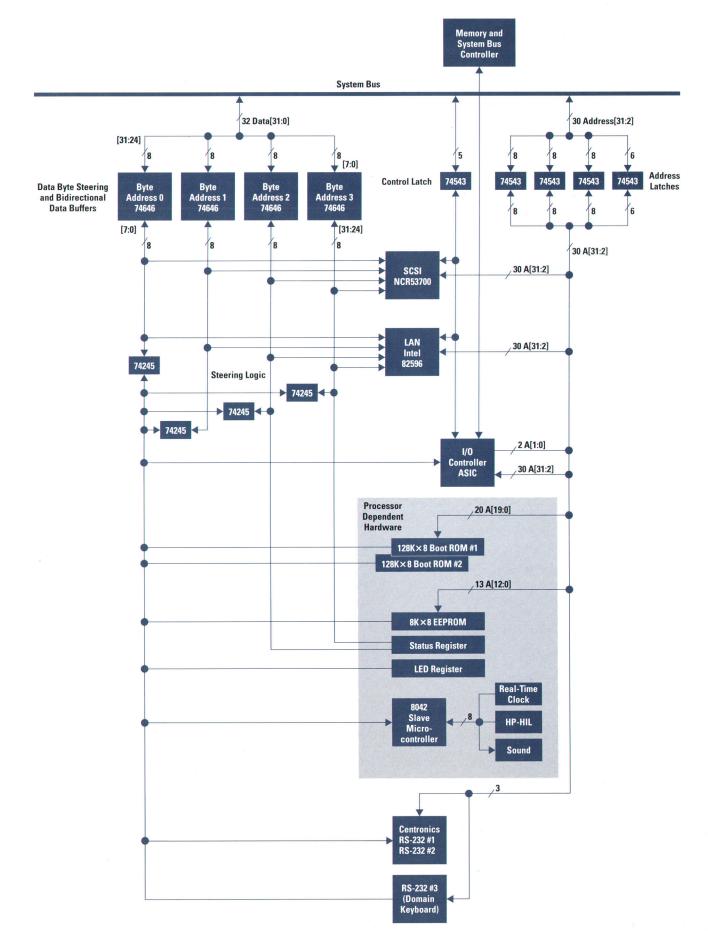

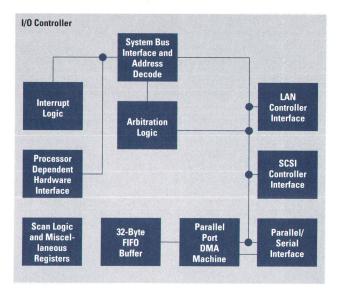

| 6  | HP 9000 Series 700 Input/Output Subsystem, by Daniel Li and Audrey B. Gore                                                                                                          |  |

| 4  | <b>Design Verification of the HP 9000 Series 700 PA-RISC Workstations,</b> by Ali M. Ahi, Gregory D. Burroughs, Audrey B. Gore, Steve W. LaMar, Chi-Yen R. Lin, and Alan L. Wiemann |  |

| 5  | HP Standard PA-RISC Test Programs                                                                                                                                                   |  |

| 56 | Simulation Toolset                                                                                                                                                                  |  |

| 9  | Debugging Tools                                                                                                                                                                     |  |

| 1  | Metrics                                                                                                                                                                             |  |

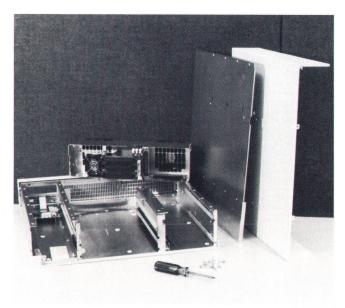

| 3  | <b>Mechanical Design of the HP 9000 Models 720 and 730 Workstations</b> , by Arlen L. Roesner and John P. Hoppal                                                                    |  |

| 9  | <b>Meeting Manufacturing Challenges for PA-RISC Workstations,</b> by Spencer M. Ure, Kevin W.<br>Allen, Anna M. Hargis, Samuel K. Hammel, and Paul Roeber                           |  |

| 5  | <b>High-Performance Designs for the Low-Cost PA-RISC Desktop,</b> by Craig R. Frink, Robert J.<br>Hammond, John A. Dykstal, and Don C. Soltis, Jr.                                  |  |

|    |                                                                                                                                                                                     |  |

Editor, Richard P. Dolan • Associate Editor, Charles L. Leath • Publication Production Manager, Susan E. Wright • Illustration, Renée D. Pighini Typography/Layout, Cindy Rubin • Test and Measurement Organization Liaison, J. Michael Gospe

Advisory Board, William W. Brown, Integrated Circuit Business Division, Santa Clara, California • Harry Chou, Microwave Technology Division, Santa Rosa, California • Rajesh Desai, Commercial Systems Division, Cupertino, California • Gary Gordon, HP Laboratories, Pala Alto, California • Iim Grady, Waltham Division, Waltham, Massachusetts • Matt J. Hatline, Systems Division, Santa Rosa, California • Bryan Hoog, Lake Stevens Instrument Division, Everett, Washington • Roger L. Jungerman, Microwave Technology Division, Santa Rosa, California • Paula H. Kanarek, Inkjet Components Division, Corvallis, Oregon • Thomas F. Kraemer, Colorado Springs, Colorado • Ruby B. Lee, Networked Systems Group, Cupertino, California • Bill Lloyd, HP Laboratories Japan, Kawasaki, Japan • Alfred Maute, Waldtham, Nalytical Division, Multham, Waltham, Microwave Technology Division, Santa Rosa, California • Paula H. Kanarek, Inkjet Components Division, Corvallis, Oregon • Thomas F. Kraemer, Colorado • Springs, Colorado • Ruby B. Lee, Networked Systems Group, Cupertino, California • Bill Lloyd, HP Laboratories Japan, Kawasaki, Japan • Alfred Maute, Waldtham, Nalytical Division, Waldbronn, Germany • Michael P. Moore, Measurement Systems Division, Loveland, Colorado, Shelley I. Moore, San Diego, California • Dona L. Morrill, Worldwide Customer Support Division, Mountain View, California • William M. Mowson, Open Systems Software Division, Chelimstord, Massachusetts • Steven J. Narciso, VXI Systems Division, Leveland, Colorado • Raj Ora, Software Technology Division, Mountain View, California • Gaiter Bibeseal, Bibbingen Instruments Division, Bibbingen, Garmanet D. Poulton, HP Laboratories, Pala Atto, California • Gaiter Ribeseal, Bibbingen Instruments Division, Routain View, California • Gaiter Ribeseal, Bibbingen Instruments Division, Routain View, California • Gaiter Ribeseal, Bibbingen Instruments Division, Corvallis, Oregon • Philip Stenton, HP Laboratories, Systems Technology Division, Corvalits, Division, State Ribeseal, Biblingen Instr

©Hewlett-Packard Company 1992 Printed in U.S.A.

| 64 | Low-Cost Plain-Paper Color Inkjet Printing, by Daniel A. Kearl and Michael S. Ard                                                                               |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

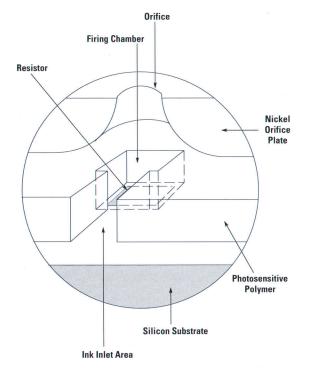

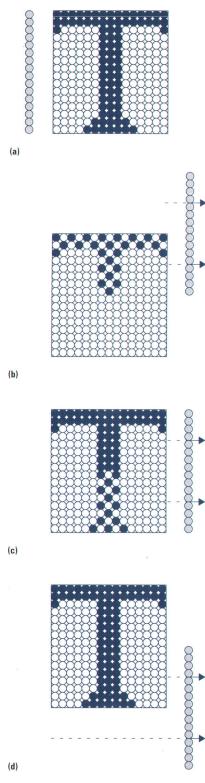

| 67 | Thermal Inkjet Review, or How Do Dots Get from the Pen to the Page?                                                                                             |

| 69 | Ink and Print Cartridge Development for the HP DeskJet 500C/DeskWriter C Printer Family, by Craig Maze, Loren E. Johnson, Daniel A. Kearl, and James P. Shields |

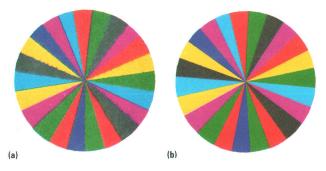

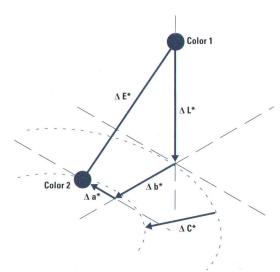

| 71 | Color Science in Three-Color Inkjet Print Cartridge Development                                                                                                 |

| 76 | Making HP Print Cartridges Safe for Consumers Around the World                                                                                                  |

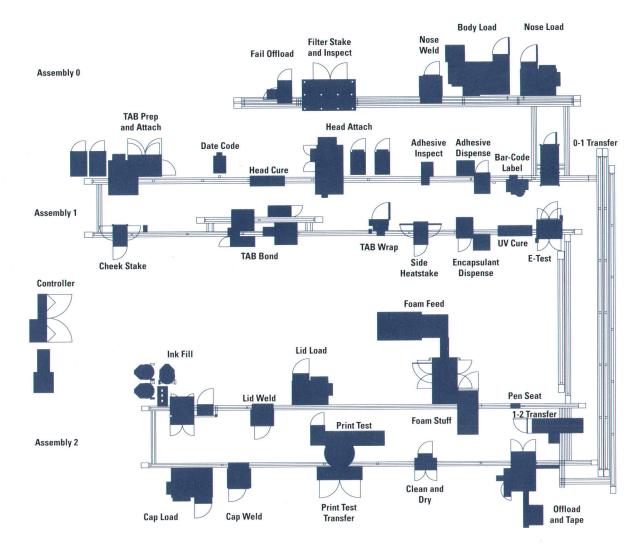

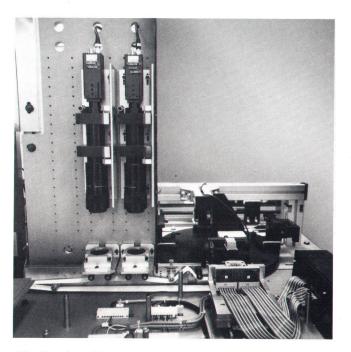

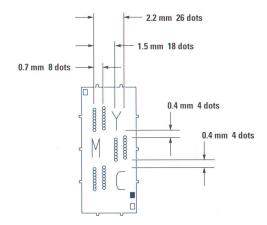

| 77 | Automated Assembly of the HP DeskJet 500C/DeskWriter C Color Print Cartridge, by Lee S. Mason and Mark C. Huth                                                  |

| 82 | Color Inkjet Print Cartridge Ink Manifold Design                                                                                                                |

| 84 | Adhesive Material and Equipment Selection for the HP DeskJet 500C/DeskWriter C Color Print Cartridge, by Douglas J. Reed and Terry M. Lambright                 |

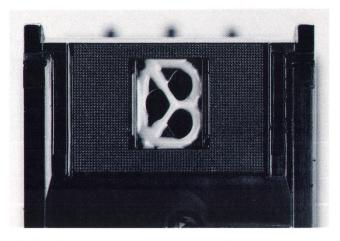

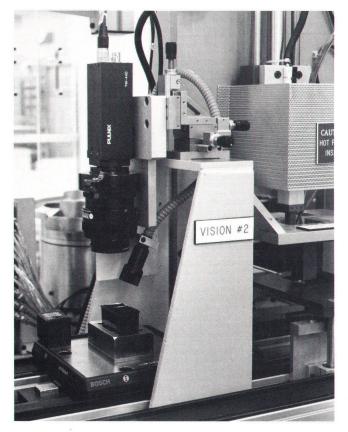

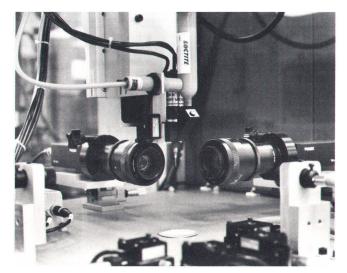

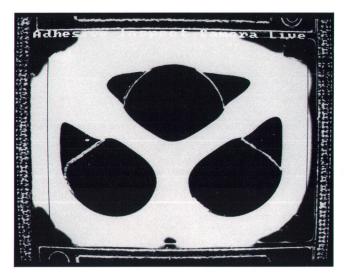

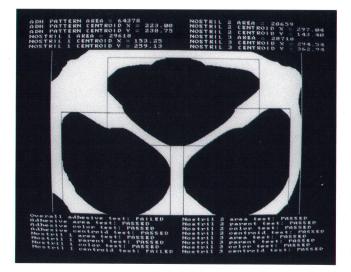

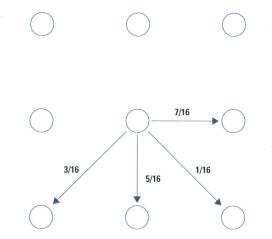

| 87 | Machine Vision in Color Print Cartridge Production, by Michael J. Monroe                                                                                        |

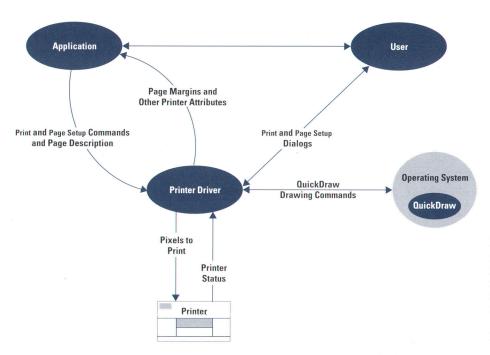

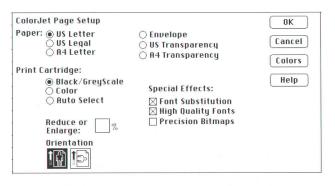

| 93 | <b>HP DeskWriter C Printer Driver Development</b> , by William J. Allen, Toni D. Courville, and Steven O. Miller                                                |

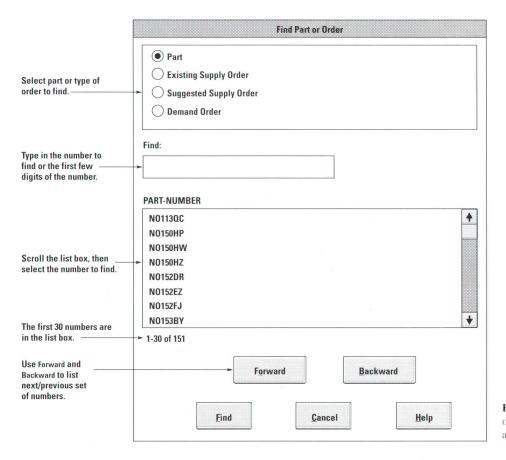

| 03 | <b>An Interactive User Interface for Material Requirements Planning</b> , by Alvina Y. Nishimoto,<br>William J. Gray, and Barbara J. Williams                   |

| 80 | HP MRP Action Manager Project Management                                                                                                                        |

|    |                                                                                                                                                                 |

# **Departments**

- 4 In this Issue

- 5 Cover

- 5 What's Ahead

- 111 Authors

The Hewlett-Packard Journal is published bimonthly by the Hewlett-Packard Company to recognize technical contributions made by Hewlett-Packard (HP) personnel. While the information found in this publication is believed to be accurate, the Hewlett-Packard Company disclaims all warranties of merchantability and fitness for a particular purpose and all obligations and liabilities for damages, including but not limited to indirect, special, or consequential damages, attorney's and expert's fees, and court costs, arising out of or in connection with this publication.

Subscriptions: The Hewlett-Packard Journal is distributed free of charge to HP research, design and manufacturing engineering personnel, as well as to qualified non-HP individuals, libraries, and educational institutions. Please address subscription or change of address requests on printed letterhead (or include a business card) to the HP headquarters office in your country or to the HP address on the back cover. When submitting a change of address, please include your zip or postal code and a copy of your old label. Free subscriptions may not be available in all countries.

Submissions: Although articles in the Hewlett-Packard Journal are primarily authored by HP employees, articles from non-HP authors dealing with HP-related research or solutions to technical problems made possible by using HP equipment are also considered for publication. Please contact the Editor before submitting such articles. Also, the Hewlett-Packard Journal encourages technical discussions of the topics presented in recent articles and may publish letters expected to be of interest to readers. Letters should be brief, and are subject to editing by HP.

Copyright © 1992 Hewlett-Packard Company. All rights reserved. Permission to copy without fee all or part of this publication is hereby granted provided that 1) the copies are not made, used, displayed, or distributed for commercial advantage; 2) the Hewlett-Packard Company copyright notice and the title of the publication and date appear on the copies; and 3) a notice stating that the copying is by permission of the Hewlett-Packard Company.

Please address inquiries, submissions, and requests to: Editor, Hewlett-Packard Journal, 3200 Hillview Avenue, Palo Alto, CA 94304 U.S.A.

# In this Issue

As promised in this space in the June issue, this issue presents the hardware design of the HP Apollo 9000 Series 700 workstations. For readers who didn't see the June issue, the Series 700 is a group of computers that surprised the workstation world early last year with a huge increase in speed over what had been available, coupled with very competitive prices. Three factors combined to give the Series 700 machines their speed advantage. One is a new version of HP's PA-RISC architecture that includes enhancements specifically aimed at improving workstation performance (the PA stands for precision architecture and the RISC stands for reduced instruction set computing). The second factor in the new computers' speed is a set of VLSI (very large-scale integration) integrated

circuit chips capable of operating at clock rates up to 66 MHz. Called PCX-S, the chipset includes a 577,000-transistor CPU, a 640,000-transistor floating-point coprocessor, and a 185,000-transistor memory and system bus controller. The third Series 700 speed enhancer (which was covered in the June issue) is a new version of the HP-UX operating system that takes advantage of the architectural enhancements and includes additional compiler optimizations to make programs run faster.

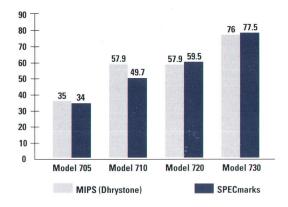

In the article on page 6, two Series 700 project managers give us an overview of the system design and performance of the HP 9000 Models 720, 730, and 750, the three original members of this product family. The PCX-S chipset is the subject of the article on page 12. The article on page 23 deals with the design of the all-important clock system that keeps everything working together, and the article on page 26 describes the built-in input/output subsystem, which provides several different standard interfaces, an audio system, and a real-time clock. Verification of the chip and system designs by computer simulation as described in the article on page 34 resulted in first silicon chips that were able to boot the operating system with no workarounds, a new record for HP. The package design of the original Series 700 work-stations is covered in the article on page 43, and the manufacturing engineering, which included setting up a new surface mount process for printed circuit board production, is discussed in the article on page 49. There are now two entry level members of this product family in addition to the three original models. The system design and performance of the HP 9000 Models 705 and 710 workstations are described in the article on page 55.

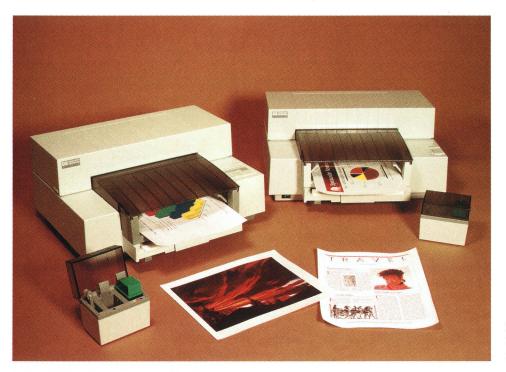

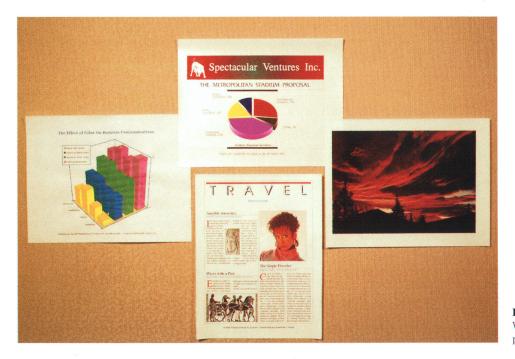

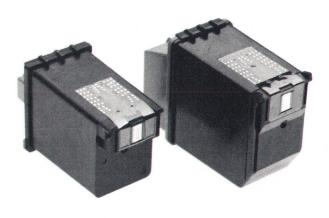

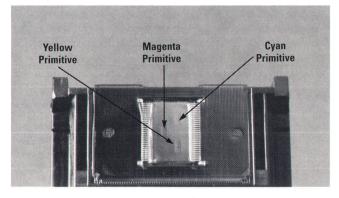

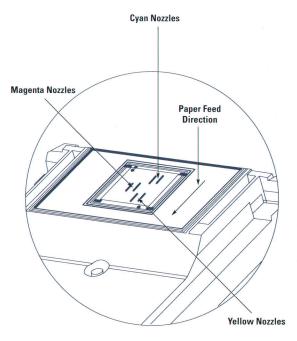

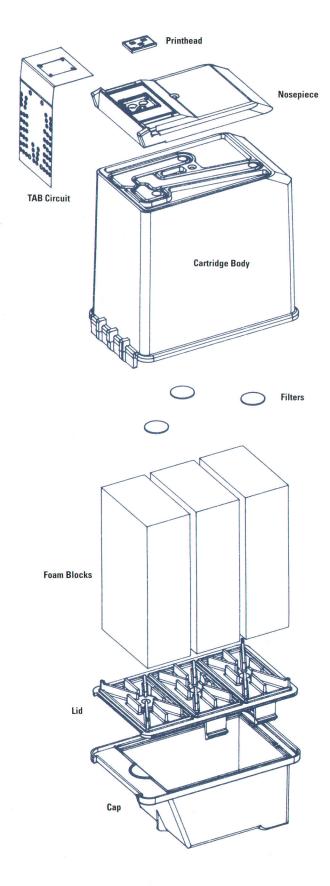

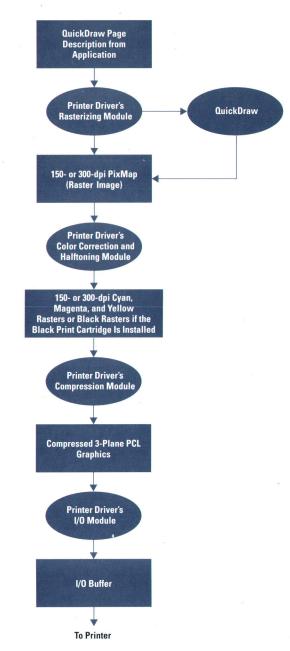

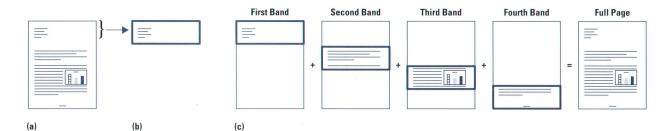

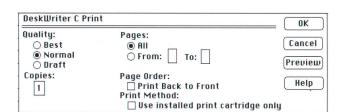

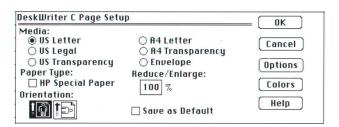

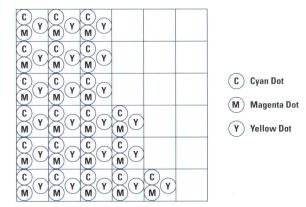

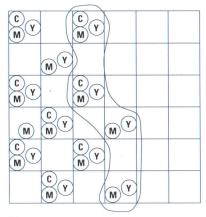

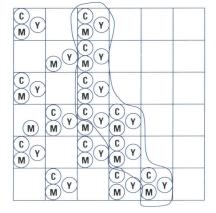

The HP DeskJet and DeskWriter printers are low-cost thermal inkjet printers that deliver 300-dot-perinch laser-quality printing on plain paper. While the original models printed only black, a color revolution has been taking place in the printer marketplace, creating a demand for an affordable, plain-paper color printer. Engineers at HP's InkJet Components Division were given the job of developing a color print cartridge for the DeskJet and DeskWriter printers, and their colleagues at the Vancouver Division were charged with adapting the printer platform to use the new cartridge. The color cartridge had to be interchangeable with the existing black print cartridge but contain three ink reservoirs instead of just one. Also, because the printers accept only one cartridge, the color cartridge couldn't depend on having a black cartridge around to help out, and had to be able to print a good black using only cyan, magenta, and yellow inks. As summarized in the article on page 64, these challenges were met, resulting in the new HP DeskWriter C and DeskJet 500C printers. The details of the design of the color cartridge and the inks are presented in the article on page 69. Manufacturing thermal inkiet print cartridges in high volume poses some formidable problems. The assembly process for the color cartridge is outlined in the article on page 77 (except for a few proprietary details). Many of the assembly steps depend on machine vision. as described in the article on page 87. Adhesives and encapsulants and the equipment to dispense them in tiny volumes to meet exacting requirements for the color print cartridge are the subjects of the article on page 84. To adapt the printer platforms to use the color cartridge, major changes were made in the software drivers. The driver for the DeskWriter C printer for Apple Macintosh computers is described in the article on page 93.

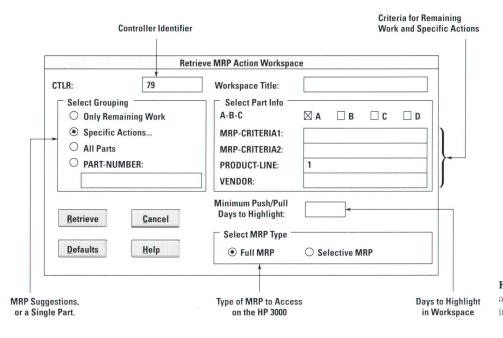

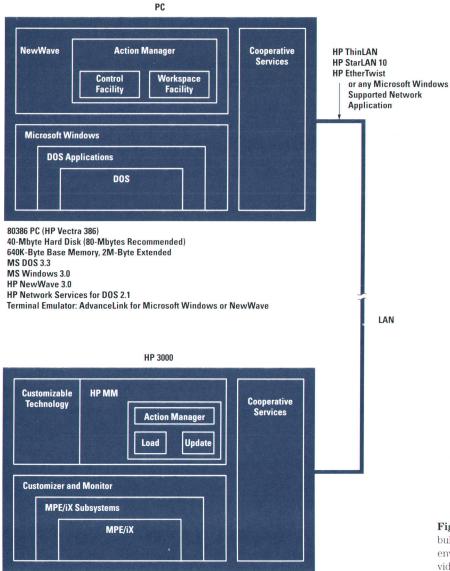

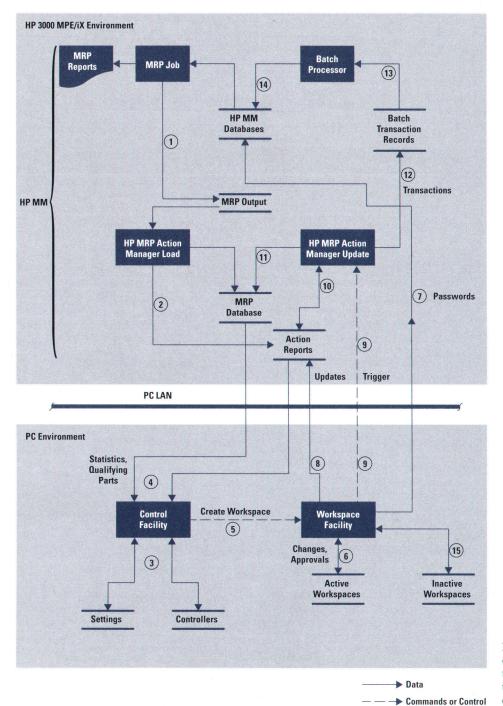

As the designers explain it in the article on page 103, "In a typical manufacturing environment, planners and buyers receive MRP (materials requirements planning) reports after running a regularly scheduled MRP program. These reports, called action reports, show suggested actions for work orders and purchase orders to meet future demand for inventory. Planners and buyers typically have to wade through mountains of paper reports to determine the suggestions they would like to act on. Then, they make any changes on paper and manually enter these changes into an MRP package. HP MRP Action Manager software automates this process." The HP MRP Action Manager software design is based on the client/ server model. The planner or buyer uses a client machine (a personal computer running the HP New-Wave environment) which communicates over a network with the server (an HP 3000 computer running the MPE/iX operating system).

R.P. Dolan Editor

# Cover

The PCX-S chipset for the HP Apollo 9000 Series 700 workstations includes a CPU, a floating-point coprocessor, and a memory and system bus controller. The chips implement the PA-RISC 1.1 architecture and run at 66 MHz.

# What's Ahead

Featured in the October issue will be:

- The HP 71500A microwave transition analyzer, a new instrument architecture for pulsed RF measurements

- The HP 4980 Series Network Advisor protocol analyzers, an expert-system-based family of instruments for digital network troubleshooting

- HP Visual Engineering Environment, a software package that allows engineers to design test programs by drawing familiar block diagrams

- The HP E3560 digital performance monitoring and remote test system, a system for surveillance of the quality of European digital telecommunications networks

- The HP HDMP-1000 gigabit-link chipset, two easy-to-use chips that implement a 1.4-gigabaud serial digital data link.

# Midrange PA-RISC Workstations with Price/Performance Leadership

The HP 9000 Models 720, 730, and 750 workstations achieve exceptional performance ratings on industry-standard benchmarks through a combination of a high CPU clock rate (up to 66 MHz) and tuning of the subsystem, compiler, and operating system designs. This article presents an overview of the hardware design.

# by Andrew J. DeBaets and Kathleen M. Wheeler

Three HP 9000 Series 700 workstation computers were introduced in March 1991. These products were milestones in three respects. First, they were the first HP PA-RISC computers designed specifically as workstations (PA-RISC is HP's reduced instruction set computer architecture). Second, the product design cycle from inception to system release was executed in only 18 months. Third, they surprised the workstation world with their unprecedented combination of price and performance.

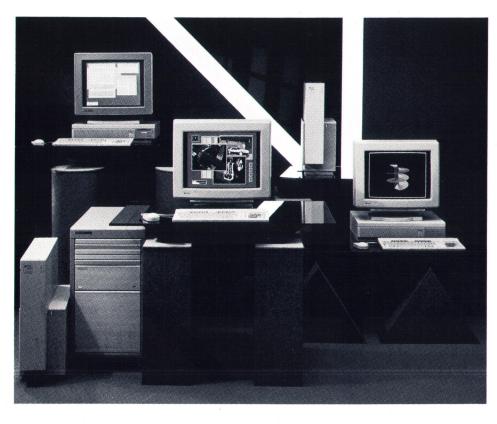

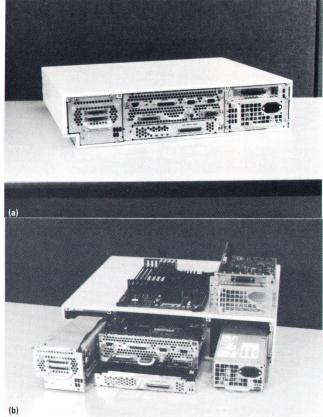

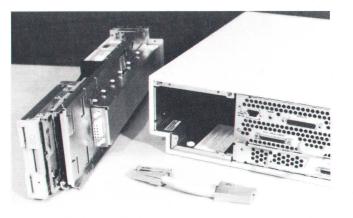

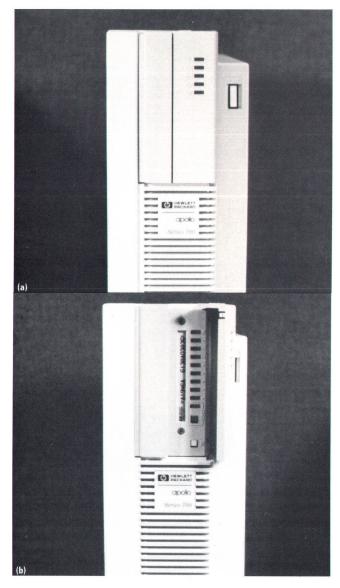

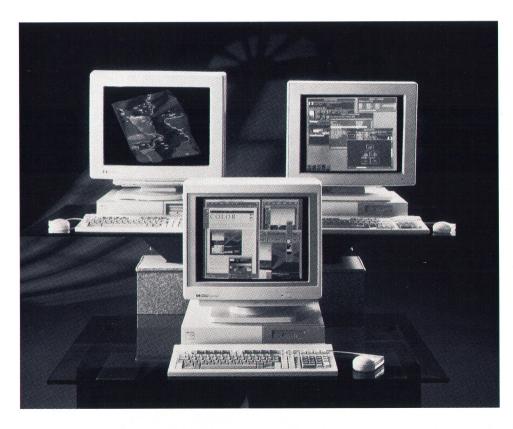

Fig. 1 shows the three workstation models. All are considered midrange computers, higher in performance than the low-end or entry-level models described in the article on page 55, which were introduced later.

The Model 720 is a 50-MHz desktop workstation. It is designed as a general-purpose workstation for CAD/CAE,

scientific, and CASE applications.\* It provides in a single enclosure a cached uniprocessor, onboard I/O, up to two internal SCSI 3.5-inch hard disks, an optional flexible disk drive, up to 128M bytes of RAM, an optional EISA (Extended Industry-Standard Architecture) interface, several graphics options, and a power supply.

The Model 730 is a 66-MHz general-purpose desktop workstation. With its additional performance, it makes a very competitive 3D graphics application engine. It is configured identically to the Model 720, except that the EISA slot is included in the base unit. The enclosures for the Models 720 and 730 are identical and are the result of new industrial design specifically for these products.

\*CAD, CAE, and CASE stand for computer-aided design, engineering, and software engineering, respectively.

Fig. 1. HP 9000 Models 720, 730, and 750 workstations.

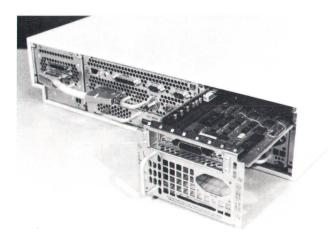

The Model 750 is a 66-MHz deskside workstation and file server designed as a high-performance 3D graphics workstation or as a workstation file server. Its enclosure is a vertical tower on a pedestal. The product design was leveraged from the HP 9000 Series 400 workstations. On a single motherboard the Model 750 provides all the functionality of the Model 730, including a cached uniprocessor, built-in I/O, and EISA interface. The memory cabability is increased to a maximum of 384M bytes. In addition, the Model 750 provides a total of four EISA slots, two graphics options, and up to four mass storage devices.

The design and implementation of these three workstations were undertaken with the following objectives, in order of priority:

- Time to market (schedule)

- Performance

- Product cost

- Development cost.

Quality was an overriding assumption of the project. The following sections provide an overview of the resulting system design, and accompanying articles in this issue give further technical details of the system components.

#### **System Overview**

The desktop Model 720 and 730 workstations are packaged in a new mechanical design. One of the key features of this package is the ease with which modules can be removed and replaced. This simplifies manufacturing and field support. The replaceable components include the CPU board, the graphics board, the system I/O board, the EISA expansion bus and EISA-compatible I/O cards, the disk drives, and the power supply. This makes it possible to define, design, and deliver component upgrade products quickly. These products can be offered as simple "board swap" upgrades to the installed base.

The deskside Model 750 workstation is packaged in a slightly modified HP Apollo 9000 Series 400 mechanical design. This existing package design offered sufficient volume, power, and cooling to contain all of the functionality of the Model 730 with increased expandability. Additional graphics, DRAM, mass storage, and EISA cards are supported within this larger package. The design of the Model 750 also allows motherboard "board swap" upgrades.

The industrial and product designs of the Model 720/730 and Model 750 packages are described in the article on page 43.

The Model 720 provides the following features:

- 50-MHz PA-RISC CPU

- 50-MHz PA-RISC 64-bit floating-point coprocessor

- 128K-byte instruction cache

- 256K-byte copyback data cache, 64 bits wide

- 8M to 128M bytes of error correcting memory

- 5-Mbyte/s SCSI II interface

- 10-Mbit/s IEEE 802.3 LAN interface

- Two RS-232 modem-control serial ports

- 350-kbyte/s bidirectional parallel port

- Audio tone generator

- HP-HIL device interface for keyboard, mouse, and other input devices

- One high-performance graphics slot, with a variety of graphics options

- One optional industry-standard EISA slot, with a variety of I/O cards

- Two integrated 3.5-inch 420-Mbyte fixed disk drives

- One optional 3.5-inch PC-compatible flexible disk drive (in place of one fixed drive).

The Model 730 increases performance and functionality over the Model 720 by adding the following features:

- 66-MHz PA-RISC CPU

- 66-MHz PA-RISC 64-bit floating-point coprocessor

- One standard EISA slot.

- The Model 750 increases performance and functionality over the Model 720 by offering the following additional features: • 66-MHz PA-RISC CPU

- 66-MHz PA-RISC 64-bit floating-point coprocessor

- 256K-byte instruction cache

- 16M to 384M bytes of error correcting memory

- Two high-performance graphics slots

- Four standard EISA slots

- Up to four mass storage devices. Two full-height 5.25-inch devices can be supported with two additional half bays that support either 3.5-inch devices or half-height 5.25-inch devices. Up to three of these bays can support removable media, and the two half bays can also be converted to support a third full-height 5.25-inch mechanism.

A configuration with entry-level graphics and EISA consists of four major printed circuit board assemblies in the Models 720 and 730 and two major printed circuit board assemblies in the Model 750. These boards contain six fully custom VLSI chips and three semicustom VLSI chips developed to implement the features listed above.

To meet the aggressive schedule objectives, the quality of the nine core chips needed to be very high. Management set a very clear expectation that the chips would be "right the first time" and provided resources to verify the designs thoroughly before tape release. As a result of the hard work of the design and verification teams, there were a number of significant successes. The first CPU chip booted the HP-UX\* operating system four minutes after it was installed in a processor board. All of the hardware was released for volume production only three months after the final VLSI chip arrived-and this VLSI chip was the heart of the system. A number of chips were released to production without changes. These successes allowed the aggressive schedule to be met. Additional details regarding the chips' design and verification can be found in the articles on pages 12 and 34, respectively.

In addition to the hardware, a common set of firmware was implemented on the three products. This firmware provides a number of functions, including self-test, booting, and console handling. A description of this firmware is provided on page 9.

#### **Processor and Memory Subsystem**

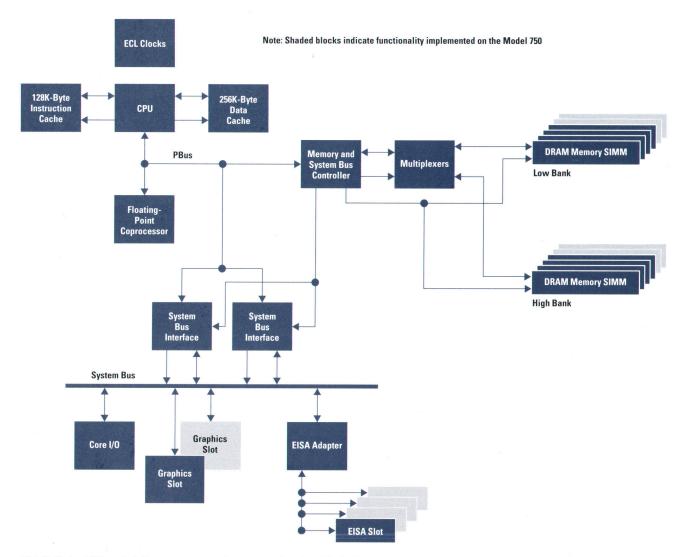

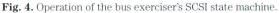

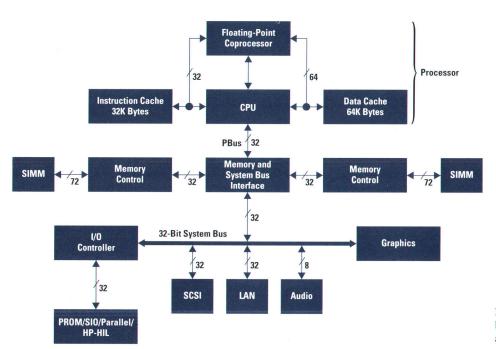

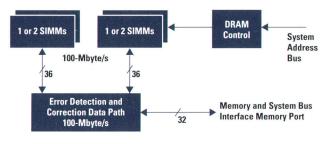

Fig. 2 is a block diagram of the processor and memory subsystem. The processor and memory designs for the Models 720, 730, and 750 are identical except for frequency. The Models 720 and 730 implement the functionality on a single printed circuit board. The Model 750 implements the same design, with I/O and EISA interface, on a motherboard twice the size of the Model 720/730 processor board.

The Model 720 CPU clock frequency is 50 MHz and the Model 730/750 CPU clock frequency is 66 MHz. Therefore, one instruction is executed every 20 ns and 15 ns, respectively. The clock system for the entire system is implemented with ECL logic and a crystal oscillator running at twice the CPU frequency. Very careful attention was paid in the design of the printed circuit boards to ensure that the clocks are synchronous at the key components of the system. Delays were calculated and adjusted in the clock trace lengths. The article on page 23 describes the design details of the clock system.

The uniprocessor design uses a VLSI CPU chip whose architecture is referred to as PCX-S (see article, page 12). The PCX-S chip is fabricated in HP's CMOS26 process and is housed in a 408-pin ceramic PGA (pin-grid array). The processor architecture is 32 bits wide. Key features include cache controllers onboard, separate TLBs (translation lookaside buffers) for data and instruction memory management, a five-stage pipeline, and test and diagnostics support.

This is the first PA-RISC processor design optimized for workstation requirements. The performance modeling looked at key requirements for the workstation marketplace. Both the floating-point coprocessor and the caches are optimized for workstation applications. The PCX-S CPU and floating-point coprocessor implement the PA-RISC 1.1 architecture, which includes enhancements to the original PA-RISC architecture resulting from a study of workstation requirements by HP and Apollo engineers. Therefore, this design represents many of the best practices of both HP and Apollo, now both represented by the HP Workstation Business Unit.

The cache is implemented as a single-level, off-chip cache memory (as opposed to many industry workstations, which implement a primary cache on the processor chip and a secondary cache off-chip). It is configured as 256K bytes of data cache and 128K bytes of instruction cache for the Models

Fig. 2. Series 700 workstation processor and memory subsystem block diagram.

720 and 730. The Model 750 is configured with 256K bytes of both instruction cache and data cache. The cache is directly mapped and has parity for error detection. The instruction cache is 32 bits wide and is organized as lines of four double words (32 bytes). The data cache is 64 bits wide and is also organized as lines of four double words (32 bytes). Parity is generated for each 32-bit word in both caches. Associated with each line in the caches is a tag, which provides 20 bits of addressing information and an additional two bits of status.  $32K \times 8$ -bit and  $8K \times 8$ -bit SRAMs are used in the Models 720 and 730, while the Model 750 uses  $64K \times 4$ -bit and  $8K \times 8$ -bit SRAMS. The SRAMs used to implement the instruction and data caches have an access time of 15 ns for the Model 720 and 12 ns for the Models 730 and 750. The fast access rates are required so that instructions and data can be input on every clock cycle.

The floating-point coprocessor was a joint design effort of HP and Texas Instruments, Inc. It has a 64-bit internal architecture and has direct access to the instruction and data caches. It is housed in a 204-pin ceramic PGA. This chip is also the result of careful implementation of previously unimplemented features to optimize workstation performance. These enhancements, described in PA-RISC 1.1 specifications, expand the floating-point instruction set.

The processor communicates with the memory and I/O subsystems via the PBus (processor bus). The 32-bit-wide PBus multiplexes the address and data lines. The transfer of data to memory and the rest of the system is controlled by a single-chip memory and system bus controller, fabricated in CMOS26 technology and housed in a 272-pin ceramic PGA. To optimize the efficiency of memory transfers, the width of the memory array was set at 144 bits (128 data bits and 16 bits of error correction code). This scheme was most effectively implemented with available hardware by creating two banks of user-installable SIMM (single inline memory module) cards.\* Each card is 72 bits wide. The current SIMM implementation uses 1M-bit DRAMs (8M bytes/SIMM) and 4M-bit DRAMs (16M bytes/SIMM). The theoretical maximum memory allowed in the system using 16M-bit DRAM technology is 1G bytes. The systems implement a fixed number of slots for SIMMs (8 slots in the Models 720 and 730 and 12 slots in the Model 750), so the actual maximum memory is less than 1G bytes. Each SIMM uses a proprietary memory interface chip to buffer the addressing of the two-bank implementation.

The memory and system bus controller chip is also a bus converter and communicates with the system bus through two proprietary system bus interface chips. The system bus is a high-bandwidth bus capable of operation up to 33 MHz (the maximum data transfer rate is 33 Mwords/s). Since the PBus is a multiplexed bus and the system bus has separate lines for the address and data signals, the primary function of the system bus interface chips is to demultiplex the PBus to the system bus and vice versa. The built-in I/O, graphics, and EISA interface all attach to the system bus.

\* The memory SIMMs are a proprietary design and do not resemble the industry-standard memory SIMM.

# HP 9000 Series 700 Workstation Firmware

The firmware for the Series 700 workstations described in the accompanying article includes what is formally known as processor dependent code (PDC) and I/O dependent code (IODC). It is a mixture of C and PA-RISC assembly language code, and it resides in two 128K-byte EPROMs on the system board. The firmware bridges the gap between the machine hardware and the operating system software by providing basic machine-specific test, initialization, and bootstrapping services.

The Series 700 firmware is a close cousin of the Series 800 firmware. The overall design and architected software interface (with a few additions) have been preserved to minimize the impact on the primary users of PDC, which include the diagnostics, the operating system loaders, and the operating system itself.

The special contributions of the Series 700 firmware are:

- · The addition of several new procedural entry points

- A revised user interface suitable for PA-RISC workstations

- A strategy for booting through the EISA interface.

For the Series 700, the primary user of the system may also function as the system administrator. Several new features were added to the firmware user interface to make system administration tasks at the PDC level easy and intuitive. Default boot and console devices can be specified through friendly module names (e.g., scsi, eisa, graphics) rather than the traditional HP NIO/CIO path notation. Another special contribution of the Series 700 firmware functionality is an optional I/O scan for potentially bootable devices.

Several new procedural entry points were developed for the Series 700 to preserve the external PA-RISC view of the I/O subsystem as seen through the PDC procedural interface. Unlike Hewlett-Packard's proprietary CIO and NIO, the Series 700 I/O modules do not reside at fixed address intervals (slots) in I/O space. That is, Series 700 I/O modules do not necessarily reside on successive 4K boundaries. For the Series 800, the operating system uses this fixed position knowledge to convert a representation of an I/O module (in the traditional bus converter, physical module, device dependent layer notation) to the corresponding start address. Many of the PDC entry points that provide auxiliary information about I/O modules require as an input parameter this hard physical address. Rather than change the PDC interface (and force all callers of PDC to change also), a special new entry point, PDC\_MEMORY\_MAP, provides the necessary translation of a logical designation of an I/O module to the hard physical address. Thus, software need deal only with the logical mapping of I/O modules and need not derive or have a priori knowledge of the actual physical address of the module.

A special strategy was derived to facilitate a boot through the EISA interface, independent of the EISA configuration file information inherent in most PC EISA boot models. This strategy involved a definition for PA-RISC EISA IODC (consisting of architected IODC with a special header and an extra entry point) for the card of interest, a new PDC entry point, PDC\_EISA, which provides machine-dependent information for the EISA IODC, and a cooperative scheme between the PDC and the operating system to allow a "cold" boot through EISA (before having run the on-line EISA configuration utility). This strategy is not exclusive to the Series 700.

The Series 700 firmware was developed on HP 9000 Model 840 and 835 computers using the PA-RISC simulator with extensions for I/O modeling. A complete simulated boot of the firmware from power-up to initial program load was achieved before arrival of first silicon. Simulation greatly reduced the time needed to bring up the firmware on the actual hardware.

> Deborah A. Savage Software Development Engineer Workstation Systems Division

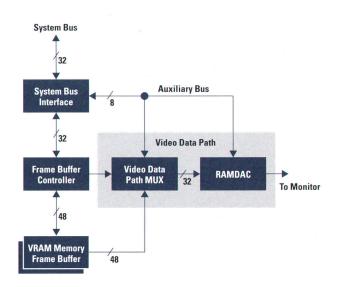

# Graphics

The Model 720/730/750 system design is optimized for graphics performance. Workstation application performance was a fundamental objective of the project and graphics is a key component. As a result, special features have been added to the memory and system bus controller chip, and the system bus specification is customized for graphics applications.

The memory and system bus controller implements a core set of functionality to optimize and thereby accelerate graphics performance on the system. The two main functions are interpolation of Z buffer and frame buffer data. Another core function is block move transfers between memory and the graphics hardware.

The drive to create a "one box on the desktop" workstation also led to the creation of a low-cost, one-board, graphics subsystem, which occupies the graphics slot configured in the Models 720, 730, and 750. The performance of this graphics option (CRX) exceeded expectations at 1.15 million 2D or 3D vectors per second (8 bit color). An article on this subsystem is planned for a future issue of this journal.

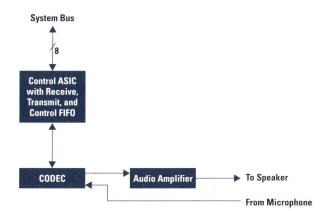

### **Built-in I/O**

One of the objectives for the I/O subsystem was to use an industry-standard I/O bus. A number of alternatives were considered, and a brief, spirited, period of discussion and analysis led to the selection of a bus from the PC world: EISA (Extended Industry Standard Architecture). A bus adapter design, using Intel's original EISA chipset, was created to connect the EISA bus to the high-performance system bus.

This selection of an industry standard bus (EISA) drove a strategy to make the PA-RISC version of the HP-UX operating system conform more closely to industry standards. This was done by modifying the operating system's I/O subsystem to provide a software interface for drivers that is much more like other vendors' systems.

The functionality provided on the EISA bus now includes IEEE 802.3 LAN, FDDI LAN, IBM token ring LAN, X.25, SNA, fast/differential SCSI, serial multiplexers, and the HP-IB (IEEE 488, IEC 625). A number of these cards and drivers are provided by independent vendors. An article on the EISA card design is planned for a future issue of this journal.

The core I/O subsystem, which is configured on the system I/O board and is independent of the EISA controller card, was selected to meet 80% to 90% of workstation users' needs without additional I/O cards. The system I/O board provides two serial ports, a bidirectional parallel port, an IEEE 802.3 LAN interface, an HP-HIL keyboard/mouse interface, and an SCSI interface. This robust offering of integrated I/O meets a wide variety of needs. The standard SCSI interface allows support for disks, DAT drives, CD-ROMs, and a PC-compatible flexible disk drive.

The core I/O subsystem also benefited from the move towards a more open operating system. This competitive focus from the operating system and networking teams provided driver support for a system I/O board design based on the latest high-performance industry VLSI controllers. The key components are new SCSI controllers from NCR (53C700, used on the system I/O board, and 53C710, used on the EISA card) and a new LAN controller from Intel (82596). These off-the-shelf devices interface efficiently and inexpensively to the high-performance system bus.

The combination of a high-performance CPU, focused I/O driver development, high-performance industry I/O controllers, and an industry-standard bus has provided impressive I/O performance. The Models 720, 730, and 750 provide sequential disk performance eight times greater than previous-generation products. NFS benchmarking (which uses networking and disk I/O) shows that configurations of the Model 750 can outperform dedicated NFS file servers. Additional details regarding the design of the core I/O subsystem can be found in the article on page 26.

## Performance

The performance of the Models 720, 730 and 750 is the result of a systems approach to creating a product that addresses the needs of workstation applications. Although the system clock rate is a factor in the performance numbers for the products, it is not the whole story. Directed design and tuning of the operating system, compilers, and subsystems, as discussed in this issue and the June 1992 issue of this journal, resulted in the industry leading performance numbers of the Series 700 workstations.

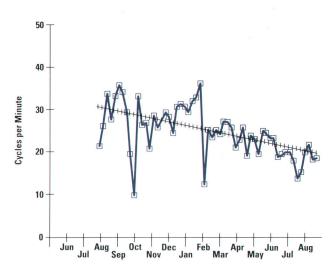

One of the workstation industry's standard measures of performance is a set of benchmarks called SPECmarks from the Systems Performance Evaluation Cooperative. This set of programs is run on the target machine and the individual results are combined to derive an overall SPECmark for the target machine. Table I shows the HP SPEC results for power desktop products as of February 10, 1992, along with the more basic MIPS (millions of instructions per second) and MFLOPS (millions of floating-point operations per second) ratings. Four of the SPEC benchmarks have little floatingpoint activity and six are floating-point-intensive. The performance ratings for these categories are listed separately as SPECint and SPECfp, respectively.

| HP 9                                                   | Table I<br>HP 9000 Series 700 SPECmark Performance       |                                      |                                         |                                       |

|--------------------------------------------------------|----------------------------------------------------------|--------------------------------------|-----------------------------------------|---------------------------------------|

|                                                        |                                                          | Model<br>720                         | Model<br>730                            | Model<br>750                          |

| SPECmark<br>SPECint<br>SPECfp<br>SPECint92<br>SPECfp92 | (rel. 1)<br>(rel. 1)<br>(rel. 1)<br>(rel. 2)<br>(rel. 2) | 59.5<br>39.5<br>78.3<br>36.4<br>58.2 | $76.8 \\ 51.2 \\ 100.6 \\ 47.8 \\ 75.4$ | 77.5<br>51.5<br>101.6<br>48.1<br>75.0 |

| MIPS<br>MFLOPS (do                                     | uble)                                                    | 57<br>17.9                           | 76<br>23.7                              | $76 \\ 23.7$                          |

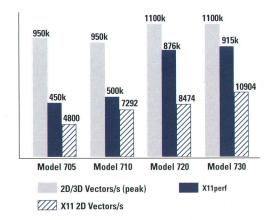

Other performance measures used to compare workstations are those tied to graphics performance. Two such metrics measure those functions contributing to X Window performance (principally 2D) and the manipulation of forms in 2D and 3D graphics applications. The metrics for the CRX option of the Models 720, 730, and 750 workstations are shown in Table II.

| Tab                   | le II                |

|-----------------------|----------------------|

| HP 9000 Series 700CRX | Graphics Performance |

|                                                               | Model<br>720CRX | Model<br>730CRX         | Model<br>750CRX  |  |

|---------------------------------------------------------------|-----------------|-------------------------|------------------|--|

| X11perf 1.2 Overall Operation<br>X11perf 1.2 General Graphics | 8,474<br>8,079  | $10,904 \\ 10,297$      | 10,904<br>10,297 |  |

| 3D Vector Performance                                         |                 | nds of 3D<br>ber Second |                  |  |

|                                                               |                 |                         |                  |  |

# Acknowledgments

The authors wish to thank Steve Foster, R&D section manager, and Russ Sparks, R&D lab manager, for their leadership and support during the development of the Series 700 products. Special thanks to the engineers of the Series 700 project, whose hard work and dedication were key to the products' success. Additional thanks are due people throughout HP and Apollo for their contributions. Finally we must thank Denny Georg for providing the competitive focus and organizational value set to allow these products to be built.

HP-UX is based on and is compatible with UNIX System Laboratories' UNIX\* operating system. It also complies with X/Open's\* XPG3, POSIX 1003.1 and SVID2 interface specifications. UNIX is a registered trademark of UNIX System Laboratories Inc. in the U.S.A. and other countries.

X/Open is a trademark of X/Open Company Limited in the UK and other countries.

# VLSI Circuits for Low-End and Midrange PA-RISC Computers

The major VLSI chips for the HP 9000 Series 700 workstations include a central processing unit with 577,000 transistors, a floating-point coprocessor with 640,000 transistors, and a memory and input/output controller with 185,000 transistors.

# by Craig A. Gleason, Leith Johnson, Steven T. Mangelsdorf, Thomas O. Meyer, and Mark A. Forsyth

Processor and memory designs for today's low and midrange engineering workstations and multiuser systems are constrained by many different, sometimes conflicting, requirements. High performance is critical for very large and computation-intensive user applications. Increasingly, customers expect more cost-effective solutions, requiring the right balance between cost and performance. In addition, product requirements dictate that processor and memory subsystems be compact, consume little power, and require a minimum amount of support hardware. The VLSI (very large-scale integration) circuits described in this paper were designed to meet these requirements and to have the flexibility to be used in a number of HP PA-RISC computers, including members of the HP 9000 Series 700 and 800 families and the HP 3000 Series 900 family.

## Overview

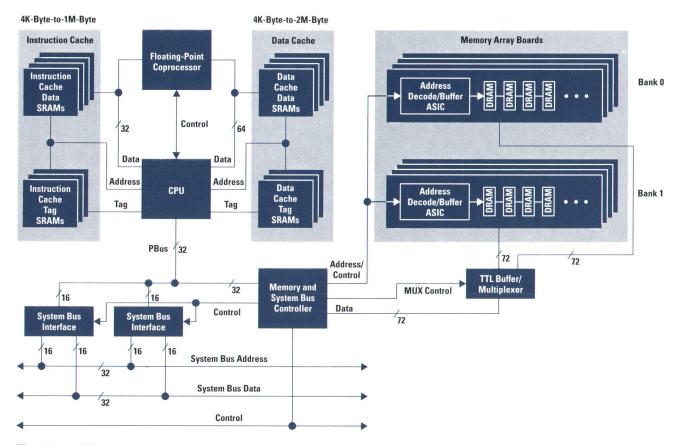

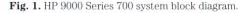

The core processor and memory subsystem for these products is shown in Fig. 1. The major VLSI chips include a central processing unit (CPU), a floating-point coprocessor (FPC), and a memory and system bus controller (MSBC). Collectively, these chips are called the PCX-S chipset. Key features of these devices are shown below:

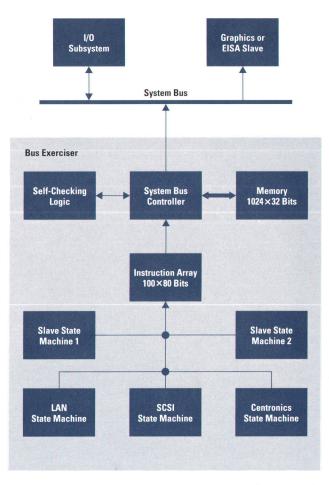

Fig. 1. Core CPU, cache, floating-point coprocessor, and memory subsystem block diagram.

| CPU                 | FPC                                                              | MSBC                                                                                                                                                                                     |

|---------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HP CMOS26<br>1.0 μm | TI EPIC-2<br>0.8 μm                                              | HP CMOS26<br>1.0 μm                                                                                                                                                                      |

| 577,000             | 640,000                                                          | 185,000                                                                                                                                                                                  |

| 14.0 by 14.0<br>mm  | 13.0 by 13.0<br>mm                                               | 9.5 by 9.5<br>mm                                                                                                                                                                         |

| 408 CPGA            | 207 CPGA                                                         | 272 CPGA                                                                                                                                                                                 |

| 66 MHz              | 66 MHz                                                           | 66 MHz                                                                                                                                                                                   |

|                     | HP CMOS26<br>1.0 μm<br>577,000<br>14.0 by 14.0<br>mm<br>408 CPGA | HP CMOS26         TI EPIC-2           1.0 μm         0.8 μm           577,000         640,000           14.0 by 14.0         13.0 by 13.0           mm         408 CPGA         207 CPGA |

#### **CPU and Cache Design**

All processor functions except for floating-point execution and cache memory storage are performed by the CPU. This chip interfaces to both the FPC and the cache memory arrays. It also includes an interface to the memory and I/O subsystem. The CPU implements HP's PA-RISC version 1.1 architecture, which includes extensions to the original PA-RISC architecture focused on enhancing workstation performance.

Because time to market was a key design focus, many features of the PCX-S CPU design were drawn from the PCX chipset used in HP's high-performance multiprocessing systems.<sup>1</sup> The design was modified to accommodate a lowercost system more closely aligned with the needs of the engineering workstation and low-end multiuser computer markets. Where the previous design employed two-way setassociative cache memories requiring VLSI support chips, the new chip is designed to interface directly to TTL-I/O SRAM chips. Tuning of the system to operate at higher frequencies with faster SRAMs was also facilitated through this change. The on-chip TLB was increased in size and made fully associative to allow the removal of the second-level TLB in the original design. New features and instructions (including the PA-RISC 1.1 extensions) were added to improve user interface performance. All proposed changes were prioritized according to their schedule impact and potential performance improvement, and those that offered the best ratio of performance improvement to design effort were chosen. Because of this schedule-driven choice of features and the high leverage from the previous chip, only fourteen months were required to reach first silicon.

Physically, the CPU is divided into seven major blocks: two data paths, two memory management units, a cache control programmable logic array (PLA), a pipeline control PLA, and an input/output block containing the various interfaces to cache memory storage and the memory and system bus controller. Several small control and logic blocks composed of standard cells and custom logic are also included. The design methodology used was "structured custom," where blocks are composed largely of library cells but are often hand-tiled and include custom circuits to enhance performance.

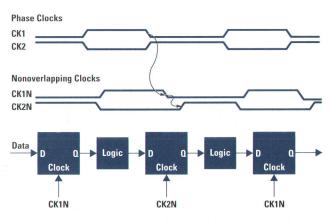

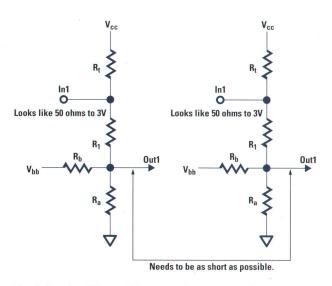

Phase clocks are used to divide each processor cycle into two halves or phases. The CPU includes three clock buffers, each fed by differential, ECL-level sync inputs (see article, page 23). The outputs of all three buffers are connected onchip to reduce clock distribution skew. Each buffer outputs two complementary signals,  $\mathsf{CK1}$  and  $\mathsf{CK2},$  representing the two clock phases.

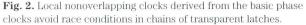

Most registers on the chip are constructed with transparent latches, which update their outputs while a clock input is true and hold the previous value while the clock input is false. These latches are more easily constructed in CMOS than edge-triggered latches. Another advantage of using the transparent latches is that in critical timing paths, the data tends to flow from one latch to another without waiting for clock edges. This technique allows the system to run at higher frequencies by spreading out timing budgets over multiple phases, rather than being limited by the slowest one-phase budget (as in an edge-triggered system). To avoid race conditions in queues of transparent latches because of overlap and distribution skew between CK1 and CK2, local nonoverlapping clocks are created (see Fig. 2).

Each integer instruction executed by the machine is processed by the CPU's five-stage pipeline. Five instructions can be processed concurrently, one in each of the various stages of execution. An instruction begins with a fetch from the instruction cache followed by a stage to decode the instruction. Branch and arithmetic stages follow, in which all arithmetic and logical operations are done, conditions are set, and branch targets are calculated. In the fifth stage the instruction is completed by writing its result to a general register.

Many architected registers are housed in the two data paths. A stack of 32 general-purpose registers acts as the first level of data storage. All integer operations use these registers for fast access to data. Load and store instructions are provided to move data between the general registers and memory. Eight space registers are used to hold the 16-bit space identifier portion of the 48-bit segmented virtual address. Various control registers are included for interrupt handling, temporary storage, data protection, real-time operation, and other tasks. All of these resources are located in the two data paths.

An interesting feature of the general registers is the addition of seven shadow registers to aid in state saving and restoring. Each shadow register is located next to a companion general register. Anytime a trap occurs, the operating system must save the current state of the machine so that it can be properly restored once control is returned to the user's

code. Normally this would require many instructions to transfer the data from the general registers to temporary storage or memory (and vice versa on returning control). All seven shadow registers can be updated in parallel while handling a trap, and likewise, the contents of the corresponding general registers can be restored simultaneously from their shadow registers on returning from the interrupt.

**Execution Unit**. At the heart of the CPU is the execution unit, which handles arithmetic and data manipulation operations. It consists of an arithmetic/logic unit (ALU), a shift/merge unit (SMU) to perform shifting and bit-field extraction operations, and various registers to feed these circuits with data and collect the results. Other processing resources include an adder for calculating branch target addresses.

The ALU is a high-speed, general-purpose arithmetic unit performing addition, subtraction, and Boolean logic operations. It includes logic to set conditions based on the results of instructions. These conditions can be tested to control branches, traps, and nullification. The ALU is fed by two input buses. Most often the input buses are driven with data from the general registers, but in some cases the required data has not yet been written to the general registers and exists only in various pipeline registers representing the results of previous ALU operations or loads. In these cases the data is bypassed around the general registers to the ALU. Using bypassing, an instruction can use the result of the previous instruction as one of its operands without causing the CPU to stall. A load followed by an immediate use of the load target as an operand will cause a single cycle penalty.

Because branches are an important component of any instruction stream, an effective branch prediction algorithm is implemented. On any program-counter-relative branch (where a positive or negative displacement is added to the current program counter to calculate the branch target), the CPU predicts that backward branches will be taken and forward branches will be untaken. Intuitively this is a good choice since most backward branches will be in multiple iterations of loops, while forward branches might be encountered in case statements, for example. Correctly predicted branches incur no pipeline penalty. An incorrectly predicted branch will cause a one-cycle delay.

**Cache Memories.** No on-chip cache memory is provided, but the CPU includes full data, tag, and address interfaces to separate instruction and data cache memories. Each of these is composed of industry-standard, asynchronous, TTL-I/O static RAMs (SRAMs), providing a wide variety of cache speed and size options. Included in the cache interfaces are tag compare circuitry, parity encoding and decoding logic, store byte merging logic, and cache fill and copyback circuits.

Given that SRAM technology is constantly improving, the system is designed to make the cache read cycle its critical path. With the 12-ns 256K-bit SRAM parts available in 1991 it is possible to build a 66-MHz system with up to 256K bytes (each) of instruction and data caches. However, with the cache access path limiting system frequency, a growth path is left open to higher frequencies simply by substituting 10-ns, 8-ns, and even faster SRAMs. An additional advantage of the SRAM-limited design is the opportunity to reduce the operating frequency and save cost by using a lower-speed SRAM part (as in the 35-MHz HP 9000 Model 705 workstation and the 32-MHz HP 9000 Model 807 multiuser system).

The cache memories are optimized for read timing, since writes occur less frequently in most code (remember, every instruction fetch involves an instruction cache read). Data cache fills take two cycles per double word, and data cache stores take three cycles, using a read-modify-write operation. Compiler scheduling is used to eliminate penalties because of conflicting loads and stores on the data cache. In cases where this is not possible, a store can result in a oneor-two-cycle penalty if either of the next two instructions is a load.

While filling the cache on an instruction cache miss operation, the CPU can execute the code as it is copied into the cache. This "cache streaming" effectively reduces the miss penalty by up to eight cycles. A similar algorithm is used on the data cache.

To provide the fastest possible cache access, a virtual address is used to index the SRAMs (this allows the CPU to access the cache before it has done a virtual-to-real address translation). The tag contains the real address of the data stored in each 32-byte cache line, as well as a "dirty" bit to indicate that the location has been modified and a "private" bit for multiprocessor support. Each processor must obtain a private copy of a cache location before modifying that location in the cache. The instruction and data caches are directmapped, again to speed up the cache access and to reduce the CPU pin count. To reduce bus traffic in multiprocessor systems, a write-back memory update policy is implemented.

A cache access is initiated by driving an address to the SRAMs (see Fig. 3). Data will return (asynchronously) roughly one cycle later, depending on the speed of the address drive and the SRAM access time. The data is collected by transparent latch receivers on the CPU. The timing of the latch clock for the incoming data is critical. If the latch clock falls too early, data will not be valid; too late, and a fast SRAM can change its data before the receiver input is shut off. This latch clock is created by inverting the CPU clock that initiates the cache access and delaying it by

Fig. 3. Cache timing circuit block diagram.

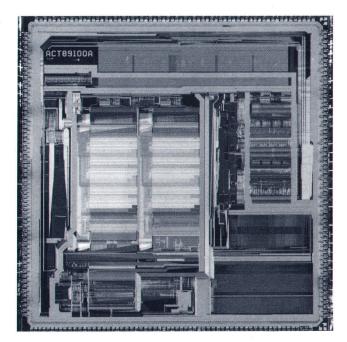

## Fig. 4. CPU chip.

means of a long printed circuit board trace. Simulations and characterization data were used to choose the correct latch clock timing for reliable, high-performance operation.

**Translation Lookaside Buffers.** Virtual-to-physical memory translation is performed by the instruction and data translation lookaside buffers (TLB). A TLB contains 96 fully associative entries, each mapping a 4K-byte page of memory. Each TLB also implements four "super-TLB," or block entries. These are used by software to map large contiguous areas of memory (up to 16M bytes), which would normally require many single-page TLB entries. One common use of the block entries is in mapping the graphics frame buffer.

On an instruction fetch a virtual address is issued to the instruction TLB. Each entry is checked to see if it contains the real translation and protection information for that address. In the case of a match, the real address is driven by the instruction TLB and compared with the real address of the incoming instruction from the cache tag. A similar process is used in the data TLB in the case of a load or store.

To perform a fully associative access in a 66-MHz cycle, the TLBs make use of several interesting circuits. Typically, a fully associative memory is composed of a contentaddressable memory (CAM), which holds the "address" of each entry, and a random-access memory (RAM), which holds the data associated with that address. In the case of the TLB, the CAM holds the virtual address of a page (space identifier and virtual page number), and the RAM holds the real page number, protection identifier, access rights, and other information specific to the entry. The virtual address for the current instruction or data access is driven to the CAM and compared with the address contained in the entry. If there is a match, the CAM causes the associated RAM entry to drive its data out of the TLB.

The TLB is required to complete its access in one phase (half cycle) so that the real address can be driven to the cache interface before the data or instruction returns from the corresponding cache access. Because of the two-part nature of the access (CAM/RAM), it was necessary to create a special timing clock to complete the CAM access and initiate the RAM access. This is done by building a dummy CAM entry that always "hits" and fires its match line. Care is taken in the chip layout to ensure that this entry always evaluates more slowly than the others. The dummy match line is buffered to create the midphase clock that will initiate the RAM access. If there is a match in any of the CAM entries, the clock will cause the select line for its RAM entry to be driven.

Entry replacement in the TLB is handled by an algorithm that provides performance similar to a least recently used policy while requiring only a fraction of the overhead. Only one bit per entry is used. The first entry whose replacement bit is zero is chosen for replacement, and following the operation its bit is set to one. If all replacement bits are ones the first entry is chosen and all other replacement bits are set to zero.

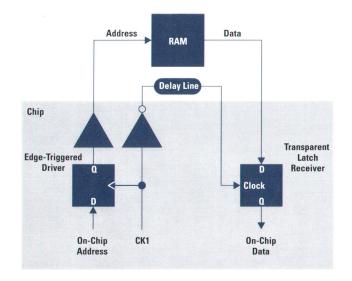

HP's high-performance CMOS26 technology was chosen for the CPU fabrication. CMOS26 offers three levels of aluminum interconnect and low-resistance silicided polysilicon and diffusion layers. Typical effective gate lengths are 0.85 micrometers for n-channel transistors and 0.88 micrometers for p-channel transistors. Fig. 4 is a photomicrograph of the CPU chip. The chip is packaged in a 408-pin multilayer PGA (pin-grid array) originally designed to support the PCX chipset. The PGA was modified for the PCX-S chip to reduce cost and reflect lower power dissipation (8 watts at 66 MHz). Multiple power and ground planes are used in the package to reduce inductance and support the high-speed switching of over 200 outputs. Power supply bypass capacitors are attached directly to the ceramic substrate of the PGA to minimize noise.

#### **Floating-Point Coprocessor**

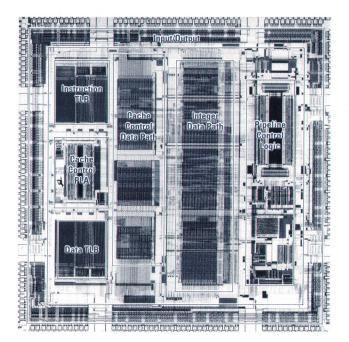

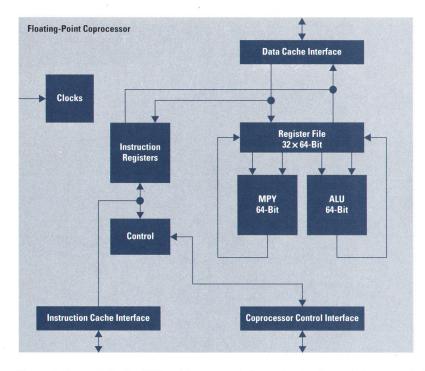

The FPC chip contains the hardware for executing floatingpoint instructions. Fig. 5 is a block diagram of this chip and Fig. 6 is a photomicrograph. The FPC chip includes an FALU data path, an FMPY data path, a large register file, ten instruction pipeline registers, and a gate array for control logic. The basic design of this chip has been described in a previous paper.<sup>2</sup>

The FPC is tightly coupled to the CPU and caches. It connects directly to the instruction cache SRAMs, so it can decode instructions as soon as they are fetched rather than waiting for the CPU to tell it what operation needs to be performed. To maintain synchronism, the FPC and the CPU keep identical copies of the processor pipeline. The FPC's direct connection to the data cache SRAMs helps minimize latency on load and store operations.

Maximizing concurrent execution of instructions was an important goal in the FPC design. There are two fully independent functional units: the FALU and the FMPY. The FALU can be performing add or subtract operations while the FMPY performs unrelated multiplies, divides, and square roots. To minimize processor pipeline stalls, the FPC has a two-entry queue for instructions that cannot execute immediately because of data dependency or resource contention. Up to ten instructions can be simultaneously pending inside the FPC.

**Fig. 5.** Floating-point coprocessor block diagram showing major blocks and buses.

These features help the FPC achieve a peak throughput of 66 MFLOPs at 66 MHz. This is very important for vectorizable applications, which have a large amount of potential parallelism to exploit. On the other hand, scalar applications have very limited parallelism potential, and for these applications, instruction execution latency is more critical for performance. The FPC has much improved latency compared to previous PA-RISC implementations. Simple add, subtract, and multiply operations execute in only three cycles. Divides require 12 cycles and square roots require 18 cycles.

**Architectural Enhancements.** A cross-functional team was empowered to identify opportunities to improve system performance through instruction set extensions. This team had representation from the processor, graphics, compilers, performance analysis, and architecture teams. Suggested extensions were validated by analyzing graphics and numerical applications, and hardware and software costs were considered as well.

The enhanced PA-RISC architecture is called PA-RISC 1.1. Enhancements to the core PA-RISC floating-point instruction set include:

- The number of 64-bit floating point registers was increased from 16 to 32. This was done to maximize the effectiveness of compilation techniques such as loop unrolling and software pipelining. These techniques can expose the concurrency present in much floating-point code, but only if the number of registers is sufficient to allow the concurrent computations to be interleaved.

- Both halves of each 64-bit register can be addressed as a 32-bit (single-precision) register. This effectively increases the number of registers for single-precision operations to 64. Moreover, a single 64-bit load or store instruction can be used to load or store pairs of single-precision values, provided they are contiguous and aligned in both memory and the register file. These improvements are particularly important for graphics code, which makes heavy use of single-precision operations.

- It is common for floating-point coprocessor implementations to have at least two independent functional units, one for multiplies and one for adds and subtracts. Two new instructions, FMPYADD and FMPYSUB, were added to execute independent operations in these two functional units in parallel. In other words, a single FMPYADD or FMPYSUB instruction can specify both a multiply and an add or subtract operation. This allows many multiply and add or subtract instructions to be fused into a single instruction.

- An unsigned integer multiply instruction was added which operates on registers in the floating-point register file. Floating-point multipliers can easily perform this operation,

Fig. 6. Floating-point coprocessor chip.

and it is much faster than the formerly used millicode routine for multiplying nonconstant integers.

The remaining enhancements are implementation dependent. These are used only in product dependent code like dynamically linked graphics libraries and the operating system, and are not available directly in application binaries. This ensures that applications will run on future machines that omit or modify these extensions.

- An inverse square root  $(1/\sqrt{x})$  instruction was added. This is frequently used by graphics code (in coordinate transformations, for example), and it is more than twice as fast as sequential square root and divide operations.

- Graphics clipping operations were accelerated by adding a 12-bit queue of comparison results and a few simple instructions to test conditions within the queue. This doubled the speed of the clipping operation for the most important "trivial accept" and "trivial reject" cases.

- A quad-word (128-bit) store instruction was added. This allows pairs of 64-bit floating-point registers to be stored in five cycles instead of the six cycles it takes using two separate stores. This is important because many codes (like memory-to-memory copy) are limited by load/store bandwidth.

#### Memory and I/O Subsystem

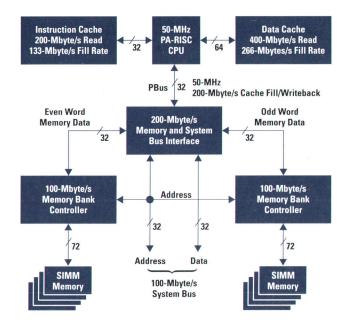

For typical application workloads, CPU efficiency is of primary importance. Cache-to-memory transfers dominate the system architecture's contribution to overall performance. The memory subsystem is optimized for low CPU-to-memory latency and bandwidth to match CPU requirements.

I/O capabilities must be sufficient to support highperformance networking and disk transfers, and must be flexible and powerful enough to support easy attachment of a wide range of devices. Transfer latencies should be minimized, and moderate-bandwidth DMA should be supported. I/O bus protocols should be simple and use standard signal levels for ease of access.

A high-performance user interface is the hallmark of workstations. High-speed transfers between the CPU or memory and the user interface provide the basis for good windowing graphics performance. Main-memory Z-buffer capability and interpolation support in the memory controller yield highperformance, low-cost 3D graphics.

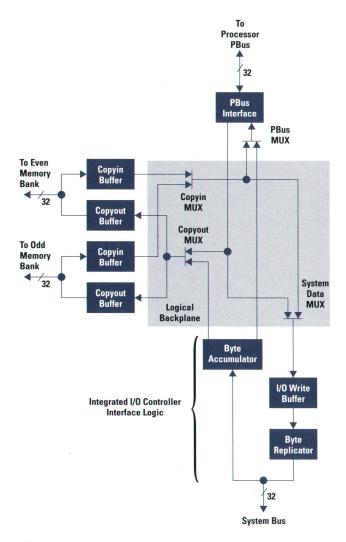

**Basic Architecture.** The above requirements led to the block diagram shown in Fig. 1. The CPU is directly connected to the memory and system bus controller by a 32-bit full-frequency bus (PBus). The memory subsystem width is 128 bits plus 16 error detection and correction bits. Standard TTL is used to multiplex this down to 72 bits into the memory and system bus controller. On the other side of the memory and system bus controller is the system bus, a non-multiplexed, 32-bit-address, 32-bit-data proprietary design.

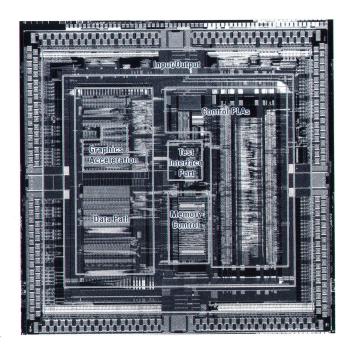

Three ASICs (application-specific integrated circuits) were designed for the memory and system bus controller subsystem. The main control ASIC, the memory and system bus controller chip (Fig. 7), is housed in a 272-pin PGA. The second ASIC is the system bus interface chip. Two of these 16-bit-wide, custom buffer parts create the system bus. They are packaged in 100-pin plastic QFPs (quad flatpacks). The third ASIC decodes memory addresses and buffers the address and control lines. It is housed in a 68-pin plastic QFP. One buffer part is used for each 18 DRAMs. The number in the system depends on the memory configuration.

**Memory and System Bus Controller Functionality.** The memory and system bus controller supports standard 80-ns DRAMs of several different densities. Cache miss latency to the first word is 155 ns, and the peak transfer rate is 260 Mbytes/s. Two 72-bit-wide banks are multiplexed and accessed in page mode to provide the necessary bandwidth.

An error detection and correction scheme is employed to control soft errors inherent in DRAM technology. An eightbit code is calculated from 64 data bits. The code used is capable of correcting any single-bit error, detecting any double-bit error, and detecting any four-bit burst error resulting from a single DRAM failure.

Memory write granularity is 64 bits (72 with error correction code). Therefore, any write of less than a double word must use read-modify-write cycles. Since cache transfers are always aligned on 32-byte blocks, read-modify-write cycles are not necessary for CPU-related transactions.

The protocol of the system bus is fundamentally a single word per transfer. A 4-word-deep buffer is used to gather DMA writes into double-word writes when possible, thus avoiding read-modify-write cycles and achieving good performance.

A single 32-byte buffer is used for temporary storage of castout cache lines on their way to memory. This buffer is controlled such that pieces of up to two lines can be present during periods of high flushing activity.

A single 32-byte instruction prefetch buffer is also implemented. Upon an instruction miss, the missing line is fetched, followed by the next line, which is placed in the

Fig. 7. Memory and system bus controller chip.

buffer. If the next instruction miss hits on the buffer, its contents are passed on to the CPU and the next 32 bytes are fetched from memory.

**User Interface Functionality.** Several features were added to the memory and system bus controller to improve user interface performance.

User interface adapters connect to the memory and system bus controller via the system bus shown in Fig. 1. This is a nonmultiplexed bus with separate 32-bit address and data paths. The separate address provides sufficient address bandwidth for the nonblock-oriented nature of some userinterface-related transfers.

Windowing and certain graphics functions benefit from highspeed transfers of data from the CPU to the user interface adapter. The CPU and the memory and system bus controller are optimized to perform these writes as quickly as possible.

User interface functions also tend to benefit from highspeed movement of data between the adapter and main memory. Special instructions and hardware were added to the CPU and the memory and system bus controller to move blocks of data to and from the user interface hardware and memory. It was intended that this functionality be available at the user level. As such it is cache coherent and uses virtual addressing.

Graphics functionality is a part of the user interface that is frequently valuable in workstation applications. Hardware to support main-memory Z-buffer, Z, and color interpolation are part of the memory and system bus controller. Good 3D rendering performance can be achieved with low-cost, simple user interface adapters.

**Miscellaneous Functionality.** EISA is the expansion bus for Series 700 workstations. A special mode is incorporated in the system bus to improve EISA transfer bandwidth.

The memory and system bus controller is the system bus host. In this role it performs arbitration, error management, interrupt management, and a few other housekeeping tasks.

**Verification**. The memory and system bus controller was the last piece of the system to enter the design phase. Unlike most other pieces of the system, there was little leverage from previous design efforts. Therefore, it was imperative to achieve high-quality silicon on the first release.

A great deal of effort was devoted to verification of the design. A checker program was developed in parallel with the ASIC models. This checker was used for stand-alone chip and system-level simulations in conjunction with an extensive suite of test vectors to verify system behavior.

First silicon was functional, and the operating system booted on the system within 36 hours of receipt of wafers from fabrication. All three memory and system bus interface ASICs were released to production with only minor metal mask revisions.

## **Technology and Architecture Choices**

RISC VLSI design teams are faced with an abundance of choices, ranging from selection of basic core technologies to fine tuning of hundreds of implementation details to give the best performance on the expected customer applications. In making these decisions, designers must consider technology and market trends, core competencies and resources of the design team, customer requirements, schedule and cost goals, and scalability of the design to meet future requirements. Given this complexity, it is not surprising that different design teams come up with radically different solutions to meet the needs of similar products.

Basic design decisions for the PCX-S chip set described in this article were made by carefully evaluating alternatives against system-level cost, performance, and schedule goals. Inputs from manufacturing, technology partners, VLSI and system designers, architects, compiler and operating system designers, performance analysts, and customers were all considered in the initial investigation stage. Some of the more important design decisions and trade-offs made are discussed in the following paragraphs.

# **PA-RISC** Architecture Extensions

A primary goal of the original PA-RISC (version 1.0) architecture definition was to support scalability across all types of computer applications and performance requirements. Before the design of the PCX-S chip set, most PA-RISC implementations had focused on meeting the needs of transaction processing, commercial, and general-purpose multiuser applications. Since PCX-S was to be an implementation also optimized for workstation applications, an extensive analysis of typical customer workstation applications and their associated performance bottlenecks was conducted early in the project (see "PA-RISC Performance Modeling and Simulation," page 21). The results of this study suggested that a small number of critical extensions to the original architecture would provide significant benefits to the customer. The evolved version of the architecture containing these extensions is known as PA-RISC version 1.1 and is fully objectcode compatible with applications developed for version 1.0.

The architecture extensions targeted three primary areas of opportunity: improved performance on floating-pointintensive technical applications, improved performance on graphics-intensive and X-windows applications, and improved performance and efficiency of the virtual memory subsystem for lower-cost implementations.

# VLSI Technology Selection and Partitioning

The design team quickly narrowed the list of VLSI technologies that could simultaneously meet all of the project goals to just one: high-speed, high-density CMOS technology. While the performance goals could have been easily met with ECL technology, the power, cost, and density penalties incurred would have limited low-cost applications of the chip set and future scalability of the design. Gallium arsenide not only had ECL's drawbacks, but also had not yet been fully proven in a high-volume microprocessor manufacturing environment.

The time-to-market goal also played an influential role in technology selection. Meeting the aggressive schedule requirements for this design required extensive leverage of existing technologies, designer expertise, tools, circuit libraries, and verification suites. For the CPU chip, the design center selected was a previous PA-RISC processor design,<sup>3</sup> which was first fabricated in early 1989. This design had been optimized for larger commercial and technical multiuser systems, including the HP 9000 Model 870 and HP 3000 Series 980 computers. The processor was fabricated in HP's 1.0-micrometer, three-level-metal, CMOS26 production technology. In addition to the CMOS26 technology, much of the implementation design, circuit libraries, and verification suites, and the multilayer ceramic package design were leveraged to decrease time to market for the new CPU design.

The floating-point coprocessor posed a more difficult challenge for the design team. Since the previous-generation CMOS processor had been designed to interface with highercost and higher-power ECL-technology floating-point units, direct leverage of this design was ruled out. It was also determined that the available resources could not support design of both the CPU and the coprocessor on the aggressive target schedule. Fortunately, a semiconductor partner with high-performance CMOS floating-point technology already well along in the design phase was found to codevelop the PCX-S floating-point coprocessor. Time to market was improved by separating the CPU and coprocessor on different chips, while industry-leading performance was achieved by adopting a tightly coupled design approach (floating-point coprocessor interfaced directly to the instruction and data caches) and designing matched, low-skew clock generation circuits on both chips.

Like most workstation designs, the memory and I/O interface functions are implemented on a separate IC. The CPU communicates with this chip over a high-speed synchronous bus, which is functionally and electrically identical to that used in other HP PA-RISC systems. This allowed the processor to be prototyped in existing systems, improving the schedule in the evaluation phase, and made the new design compatible with a variety of other memory systems optimized for different types of applications. Like the CPU and floating-point coprocessor designs, the memory interface IC design used a structured custom approach. Among other benefits, this allowed the inclusion of new features such as embedded graphics acceleration logic.

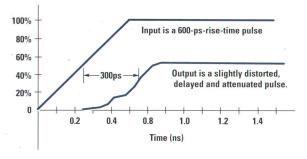

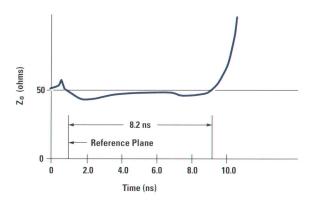

### **High-Frequency Design**